Loading…

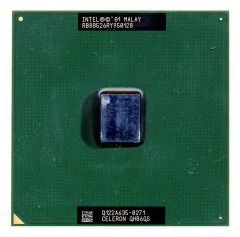

Celeron 950 Mhz ES

Week 22, Year 2001RB80526RY950128 / Q122A635-0271 / CELERON QHB6QS

Based on the Coppermine core built with the Intel's 0.18µm process, the P-III Celeron comes with 128 Kb of L2 cache instead of 256 Kb. It uses an FSB clock of 100 MHz and a multiplier of 9.5x. This qualification sample was built in late May 2001. The commercial Celeron 950 were introduced in August 2001. This sample had a completly unlocked multiplier, from 6x to 12x